简历

案例介绍

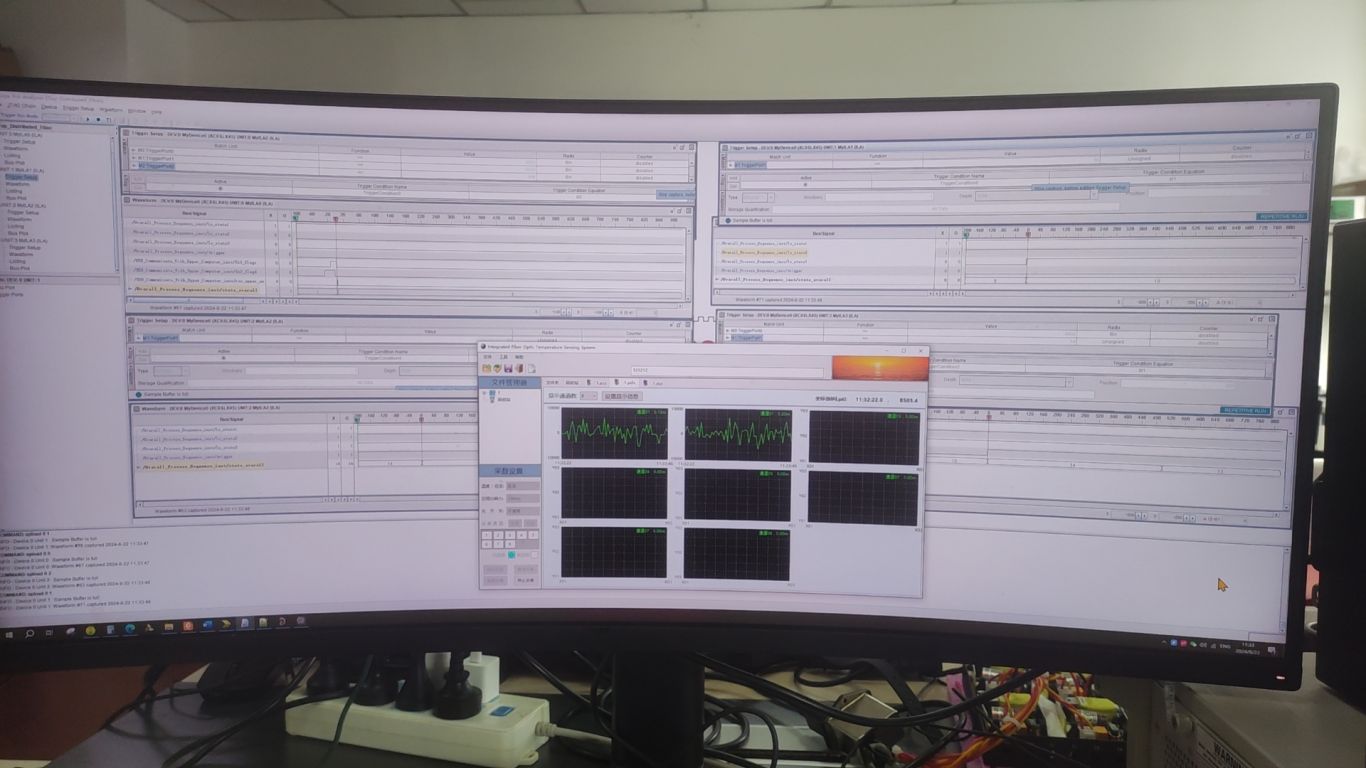

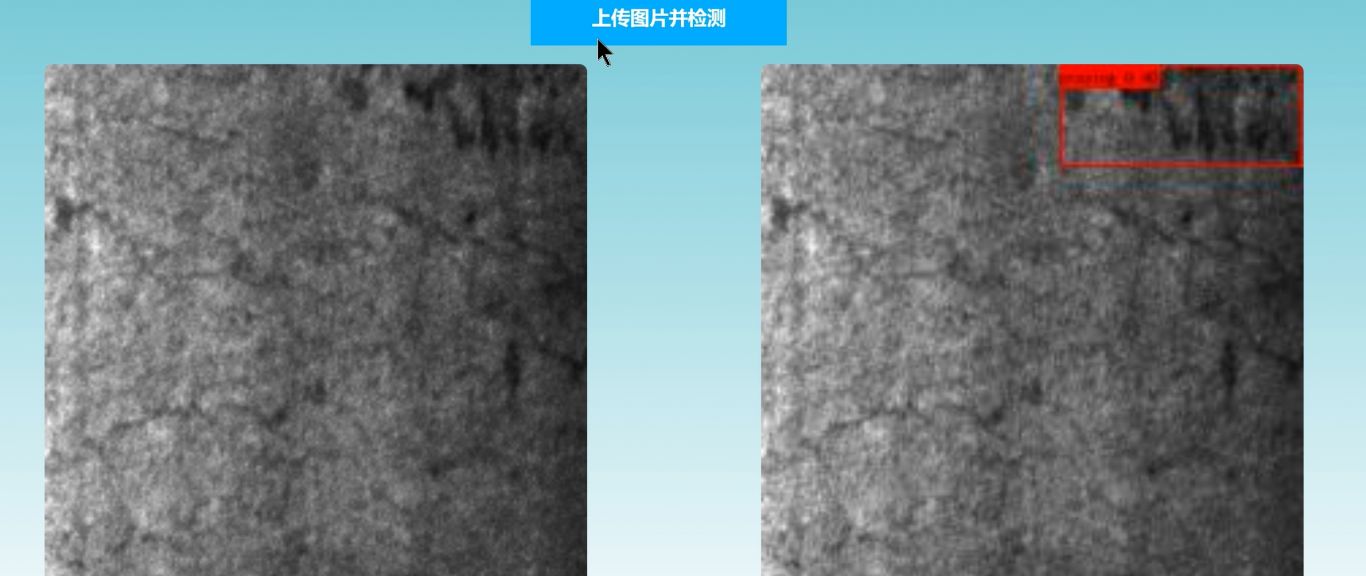

FPGA作为主控模块, 分别与USB3.0进行通信, uart与ARM进行通信, 采集ADC芯片的数据, 将数据通过AXI_FULL协议缓存到

DDR3缓存模块当中。 上位机发送修改校正系数的命令, 则FPGA会往EEPROM里面写校正系数。 上位机发送读取校正系数的命

令, 则FPGA会往EEPROM里面读校正系数。 上位机发送修改数据采集的命令, FPGA将这个命令通过uart协议透传给ARM上,

ARM根据命令去启动外部的硬件, 如果外部的硬件都成功启动, 则进行ADC数据采集, 否则发送对应的错误码。 采集点数大概为

200万个点左右, 最终FPGA将这些数据打包, 通过USB3.0的发回给上位机。

案例图片